JEVeC DAY 2019

開催概要

| 名 称 | JEVeC DAY 2019 |

|---|---|

| 日 時 | 2019年12月17日(火)10:00 – 19:00 (受付開始:9:30) |

| 会 場 | 川崎市産業振興会館 〒212-0013 神奈川県川崎市幸区堀川町66番地20 TEL: 044-548-4111 ※ 現在、川崎市産業振興会館では外壁等の改修工事が行われています。 あらかじめご了承ください。 |

| 主 催 | 日本EDAベンチャー連絡会(JEVeC) |

| 企画・運営 | JEVeC DAY 2019 実行委員会 |

| 入場料 | 無料 |

| 問い合わせ | jevecday-info (at) jevec (dot) jp までメールにてお問い合わせください。 |

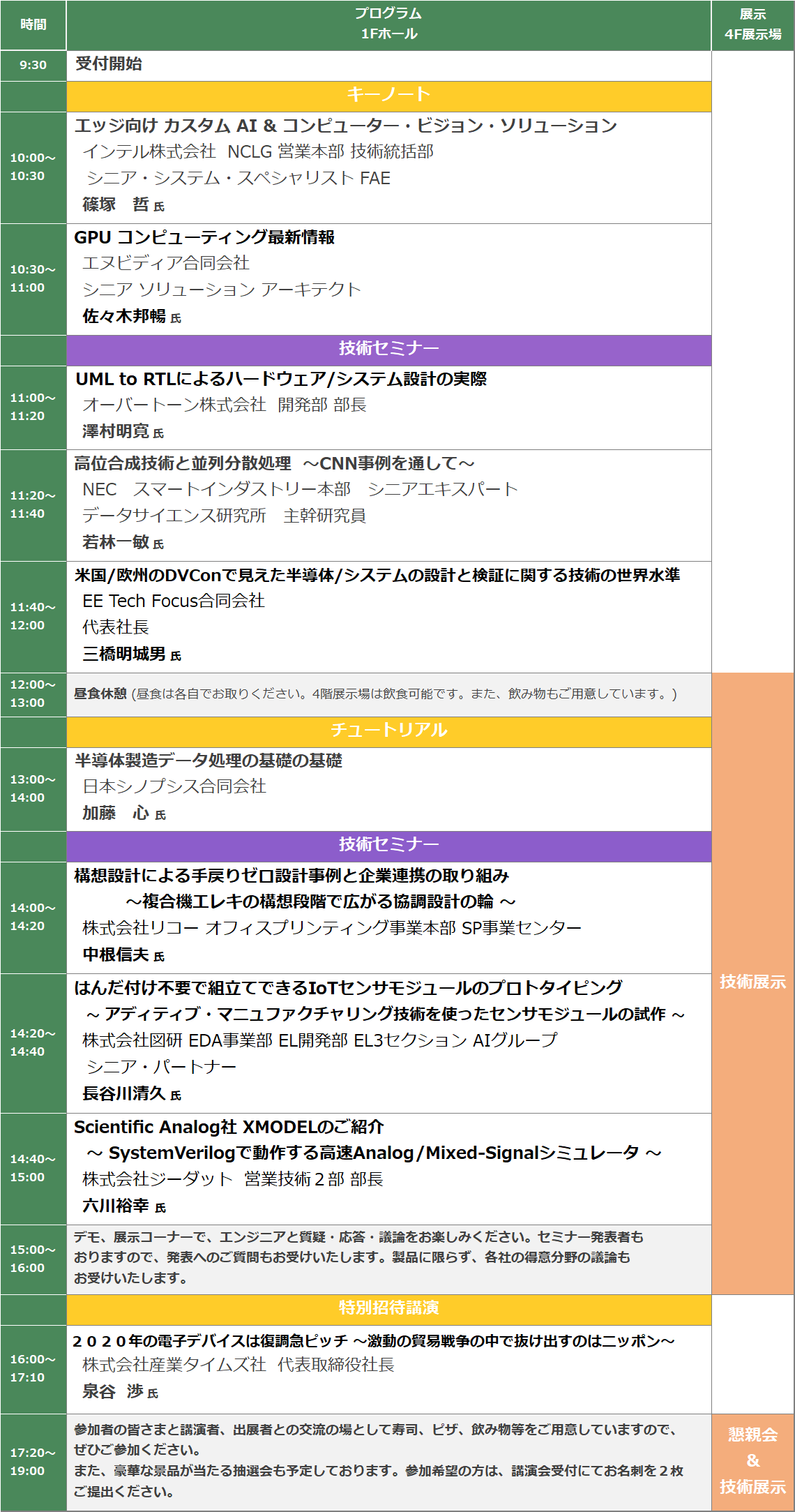

タイムテーブル

講演会(1階ホール)

キーノート

10:00~10:30 |

篠塚 哲 氏インテル株式会社

|

エッジ向け カスタム AI & コンピューター・ビジョン・ソリューション

FPGA はカスタマイズされたシステム開発に重要な役割を果たし、差別化された高性能な機能システムの構築に必要な計算、メモリー、インターフェースを提供します。 |

10:30~11:00 |

佐々木邦暢 氏エヌビディア合同会社

|

GPU コンピューティング最新情報

エッジデバイスからスーパーコンピューターまで、規模を問わず統一されたアーキテクチャが開発者の生産性を高めるGPUコンピューティング。昨今は機械学習領域での活用がますます広がっています。 |

チュートリアル

13:00~14:00 |

加藤 心 氏日本シノプシス合同会社 |

半導体製造データ処理の基礎の基礎半導体製造工程においては、上流設計工程で作成されたデザインデータを元にOPC(光近接効果補正)などの補正処理が行われ、最終的にリソグラフィ用のマスクデータが作成される。近年の回路微細化に伴い、高度な補正計算技術が必要とされ、またデータボリュームの増大に対応するため、分散並列処理などの技術が幅広く適用されている。さらに、各種製造装置(計測・検査・分析装置)に対応したデータ処理技術が求められ、多くのソフトウェアベンダーが技術を競い合っている。 |

特別招待講演

16:00~17:10 |

泉谷 渉 氏株式会社産業タイムズ社

|

2020年の電子デバイスは復調急ピッチ

|

技術セミナー(1階ホール)

午前

11:00~11:20 |

UML to RTLによるハードウェア/システム設計の実際

ロボットやエッジ・IoT機器などの、品質/安全性の向上や付加価値の創造は様々な分野のエンジニアの共同作業が必須です。これをどのように実現することができるか、実際に設計ドキュメントの質を高めて仕様の共通理解を促進し、成果物のメンテナンス性や再利用性が向上する設計例をもとに紹介します。 |

澤村明寛 氏オーバートーン株式会社

|

11:20~11:40 |

高位合成技術と並列分散処理

|

若林一敏 氏NEC

|

11:40~12:00 |

米国/欧州のDVConで見えた半導体/システムの設計と検証に関する技術の世界水準DVConはSystemVerilog、UPF、PSL、UVM、PSSなど、IEEEへの寄贈なども視野に、業界で求められる標準規格や言語、手法を策定してきた団体 – Accellera System Initiativesが主催するカンファレンスで、ユーザの論文セッションを中心に、ポスターセッション、パネルディスカッション、チュートリアル、ワークショップ、展示などで構成されています。 |

三橋明城男 氏EE Tech Focus合同会社

|

午後

14:00~14:20 |

構想設計による手戻りゼロ設計事例と企業連携の取り組み

|

中根信夫 氏株式会社リコー

|

14:20~14:40 |

はんだ付け不要で組立てできるIoTセンサモジュールのプロトタイピング

|

長谷川清久 氏株式会社図研

|

14:40~15:00 |

Scientific Analog社 XMODELのご紹介

|

六川裕幸 氏株式会社ジーダット

|

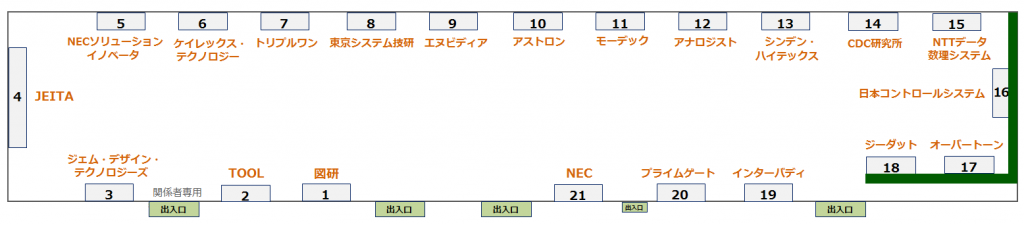

出展社一覧(4階展示場 14:00-17:30)

懇親会&抽選会 ↓ I:招待展示 G:一般展示 M:会員展示

| 1 | (株)図研 | CR-8000 Design Force システムレベルマルチボード設計環境 単体基板はもとより複数基板間を連携したマルチボード設計、異なるテクノロジ部品を統合するLSI/PKG/PCB協調設計、電気設計者向けエレメカ協調設計に対し、3D技術を取り入れ直観的でわかりやすい1プラットフォーム設計環境CR-8000 Design Force設計環境をご紹介します。 また、Design Forceで設計を行い実装、2019年9月に一般公開されたIoT機器を簡単に作れる小型プラットフォーム「Leafony」の展示を行います。 | G |

| 2 | TOOL(株) | 大規模データの超高速読み込みと表示に加え、他社製ツールや装置との親和性の高さから、DRC/LVS検証結果の解析や故障解析装置との連携によるCADナビゲーション機能としても活用いただけるICデザイン視覚検証ツール「LAVIS-plus」をデモを交えてご紹介します。 さらに、フルチップの電源網の抵抗値計算や指定した2点間の抵抗値計算、および電流, 電流密度, 電位といった計算を高速に行う高速抵抗値計算&解析ツール「RSCALC」もご紹介します。 | M |

| 3 | (株)ジェム・デザイン・テクノロジーズ | ICパッケージとプリント基板のための物理プランナー GemPackage を展示します。 GemPackageは電子機器メーカーと半導体ベンダーとの協調設計を製品構想段階から実施するために最適なツールです。 また、製品構想段階のフロー全体を改善するための「IEC63055/IEEE2401活用Web環境」(仮称、開発中)を参考展示します。 | M |

| 4 | 電子情報技術産業協会(JEITA) | ~競争と共創による業界発展の仕掛け~ 最新半導体設計技術動向 Accellera Systems Initiative による設計標準紹介。 電子機器開発手法のフロントローディング化、特にMBE・MBSE関連の説明を行います。 | G |

| 5 | NECソリューションイノベータ(株) | プリント基板のEMIノイズ対策ツール DEMITASNX プリント基板設計における EMIノイズ対策ソフトウエア「DEMITASNX」をご紹介します。 最新バージョン(Ver6.0)で搭載された EMIチェック結果 AI絞込み機能をはじめ、プリント基板の設計段階での効果的なノイズ対策についてご説明いたします。 | M |

| 6 | ケイレックス・テクノロジー(株) | 現在、半導体業界でも導入が進み始めたPLM(製品ライフサイクル管理システム)を、紹介をします。プロジェクト管理ツールを通した設計成果物の管理、成果物間のトレーサビリティ管理を行います。 弊社では、電子デバイス業界に特化したPLMソリューション提供を手掛けています。 | M |

| 7 | 株式会社トリプルワン | 株式会社トリプルワンが提供する、フルターンキーサービスについて展示します。 | G |

| 8 | (株)東京システム技研 | 誰でも簡単に使えるAI需要予測サービス「est! forecast」をご紹介します。 AIがお客様のデータごとに最適な予測モデルを自動で構築するので、専門知識がなくても簡単に売上や出荷量、来店客数などの予測ができます。また、気象情報やお客様がお持ちのキャンペーン情報なども予測に活用できます。月額のクラウドサービスなので初期費用が不要で、どなたでも手軽にご利用いただける需要予測サービスです。 | M |

| 9 | エヌビディア(同) | NVIDIA ブースでは組込み向けエッジ コンピューティング プラットフォームであるJetsonに製造業向け自動光学検査(AOI: Automated Optical Inspection)アプリケーションを実装したデモンストレーションを展示いたします。ディープラーニングを活用した次世代の製造業向け自動検査ソリューションの一例としてその可能性をご覧いただけます。 | I |

| 10 | (株)アストロン | 故障解析、配線リペア用CADナビゲーションの展示を行います。微細化・大規模しているICやメモリ等の故障個所を容易に見つける為の機能、特性向上の為の配線リペアの機能等の概要説明及びデモを行います。また、複数台使用される光学顕微鏡・電子顕微鏡間でのデータ受け渡しによるメリットについてもご説明いたします。 | M |

| 11 | (株)モーデック | 回路シミュレータの活用を促進し、フロントローディング化を加速する、オンデマンド型SPICEモデルライブラリサービス Model On!と、モデル検索システム:Model On! Searchを紹介します。 | M |

| 12 | (有)アナロジスト | 当社はICレイアウトDRC/LVS検証ツールとして雷切(らいきり)を出展致します。雷切は標準的なルールファイルをスクリプト変換等の手間を経ることなく、直接読み込んで処理します。GUIベースのシンプルな操作でユーザー負担を低減するよう配慮されており、インストールも容易です。従来多額の資金を要したICレイアウト設計環境をSOHOレベルの投資でも導入可能にし、作業委託を容易にするレイアウト環境提案をさせて頂きます。 | M |

| 13 | シンデン・ハイテックス(株) | お客様のアイデアを実現する「ICファウンドリサービスおよびフルターンキーサービス」をご紹介します。 | G |

| 14 | (株)CDC研究所 | 株式会社CDC研究所が提供する、エンジニア向けAll in Oneクラウドの概要およびシステムのデモを展示します。 | M |

| 15 | (株)NTTデータ数理システム | 3次元形状計算・評価ツール「ParadiseWorld-2」について紹介します。ParadiseWorld-2は、GDS-IIデータとプロセスフローから、電子デバイスの3次元形状を高速に生成し、それを可視化することで、出来上がり具合を評価できます。また、LCR抽出ツールを用いて、電気特性も評価することができます。本展示では、ParadiseWorld-2の詳細と最新情報についてご説明いたします。 | M |

| 16 | 日本コントロールシステム(株) | 半導体デバイス製造分野では、EUV リソグラフィの本格適用、マルチビームマスク描画装置の普及に伴い、更なるパターンの微細化とデータ量増加が進んでおり、フォトマスク製作時のデータ処理においても、プロセス補正技術の重要性と TAT 削減への要求が高まっています。 フォトマスク製作をサポートする弊社ソフトウエア「NDE Mask Manufacturable Suite (NDE-MS)」についてご紹介致します。 | M |

| 17 | オーバートーン(株) | ロボットやエッジ・IoT機器の開発において、品質・安全性の確保や付加価値の創造は必須です。働き方改革を進めつつ、これらを実現するには設計の生産性向上が必要不可欠です。 オーバートーン株式会社は、中核部品であるLSI開発に対して、仕様検討段階からオープンなUMLを活用し生産性が向上する設計ツール(NSL Overture)を提供。今後の人材不足の時代に対し、開発の生産性をどうあげれば良いのか、一つの解決策を事例ベースに説明します。 | M |

| 18 | (株)ジーダット | ジーダットが提供する半導体設計ソリューション群から、ScientificAnalog社のSystemVerilogをベースに動作するアナログ/ミックスド・シグナルシミュレーションツール「XMODEL」、Diakopto社、Dorado社、FishTail社、Fractal社、ProPlus社、SymplifyDA社など世界から集めた先端ツール群、さらにSiliconCreations社、Truechip社、AgileAnalog社などの各種先端IP製品、そしてジーダットの最新版のSX-Meisterシリーズ製品を紹介します。 | M |

| 19 | (株)インターバディ | (株)インターバディは、電子機器開発向けソリューションを提供しています。 仮想検証向けSystemCモデル(SyDAPmodel)、半導体設計環境、組込システム開発環境を展示します。Raspberry Pi にて FM4評価ボードとのI/Fとスライドショーの実演も行います。 詳しくはこちらをクリック | M |

| 20 | (株)プライムゲート | プライムゲートのRISC-V設計検証サービスをご紹介します。Efinix Trion FPGAにRISC-Vを組込んだデモボードを展示予定です。 | M |

| 21 | NEC | 高位合成ツールCyberWorkBenchとC/C++設計受託 C/C++とSystemCから、対象のFPGAやASICに最適化したRTLを合成するツールの最新機能のご紹介と、AIや画像処理、ネットワーク処理等のC言語レベル受託設計サービスの紹介を行います。また、学習済みCNNをFPGAで実行するデモをご紹介します。 | M |